# 22W BRIDGE / STEREO AUDIO AMPLIFIER WITH CLIPPING DETECTOR

- VERY FEW EXTERNAL COMPONENTS

- NO BOUCHEROT CELLS

- NO BOOSTRAP CAPACITORS

- HIGH OUTPUT POWER

- NO SWITCH ON/OFF NOISE

- VERY LOW STAND-BY CURRENT

- FIXED GAIN (20dB STEREO)

- PROGRAMMABLE TURN-ON DELAY

- CLIPPING DETECTOR

#### **Protections:**

- OUTPUT AC-DC SHORT CIRCUIT TO GROUND AND TO SUPPLY VOLTAGE

- VERY INDUCTIVE LOADS

- LOUDSPEAKER PROTECTION

- OVERRATING CHIP TEMPERATURE

- LOAD DUMP VOLTAGE

- FORTUITOUS OPEN GROUND

- ESD

# **DESCRIPTION**

The TDA7360 is a new technology class AB Audio Power Amplifier in the Multiwatt<sup>®</sup> package designed for car radio applications.

Thanks to the fully complementary PNP/NPN output configuration the high power performance of the TDA7360 is obtained without bootstrap capacitors.

A delayed turn-on mute circuit eliminates audible on/off noise, and a novel short circuit protection system prevents spurious intervention with highly inductive loads.

The device provides a circuit for the detection of clipping in the output stages. The output, an open collector, is able to drive systems with automatic volume control.

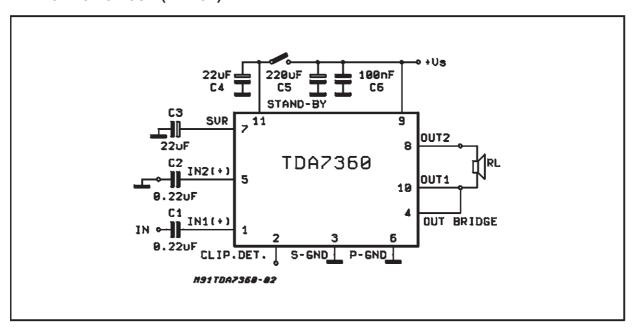

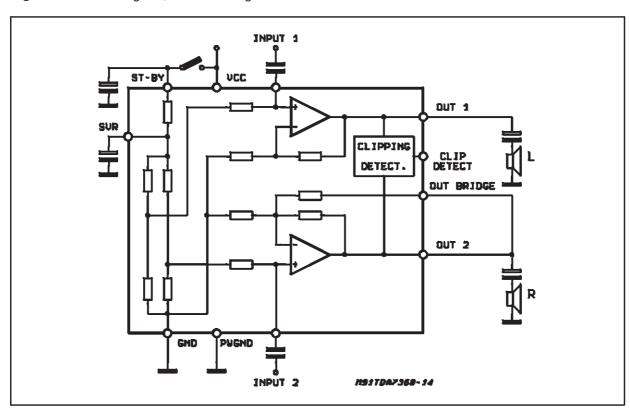

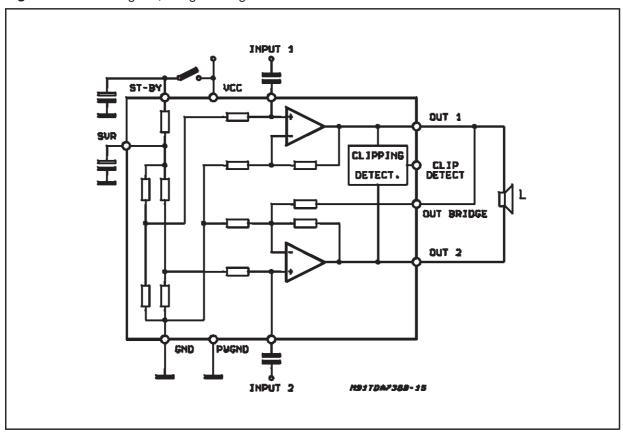

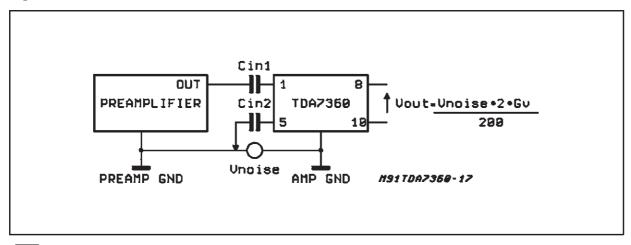

#### **APPLICATION CIRCUIT (BRIDGE)**

October 1998 1/22

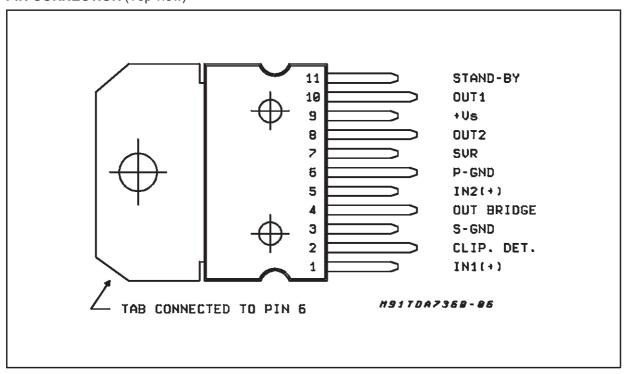

# PIN CONNECTION (Top view)

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                     | Test Conditions | Unit |

|------------------|-----------------------------------------------|-----------------|------|

| Vs               | Operating Supply Voltage                      | 18              | V    |

| Vs               | DC Supply Voltage                             | 28              | V    |

| Vs               | Peak Supply Voltage (for t = 50ms)            | 50              | V    |

| lo               | Output Peak Current (non rep. for t = 100μs)  | 5               | Α    |

| I <sub>o</sub>   | Output Peak Current (rep. freq. > 10Hz)       | 4               | Α    |

| P <sub>tot</sub> | Power Dissipation at T <sub>case</sub> = 85°C | 36              | W    |

| $T_{stg}T_J$     | Storage and Junction Temperature              | -40 to 150      | °C   |

# **THERMAL DATA**

| Symbol                 | Description                          | Value | Unit |

|------------------------|--------------------------------------|-------|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case Max | 1.8   | °C/W |

**ELECTRICAL CHARACTERISTICS** (Refer to the test circuits,  $T_{amb} = 25$  °C,  $V_S = 14.4$ V, f = 1KHz unless otherwise specified)

| Symbol         | Parameter                     | Test Condition                | Min. | Тур. | Max. | Unit |

|----------------|-------------------------------|-------------------------------|------|------|------|------|

| Vs             | Supply Voltage Range          |                               | 8    |      | 18   | V    |

| I <sub>d</sub> | Total Quiescent Drain Current | stereo configuration          |      |      | 120  | mA   |

| $A_SB$         | Stand-by attenuation          |                               | 60   | 80   |      | dB   |

| $I_{SB}$       | Stand-by Current              |                               |      |      | 100  | μΑ   |

| Ico            | Clip Detector Average Current | Pin 2 pull up to 5V $d = 1\%$ | ,    | 70   |      | μА   |

|                |                               | with $10K\Omega$ d = 5%       |      | 130  |      | μΑ   |

| TEREO          |                               | •                             |      |      |      |      |

|                |                               |                               |      |      |      |      |

| Po              | Output Power (each channel) | $d=10\%$ $R_L=1.6\Omega$ $R_L=2\Omega$ $R_L=3.2\Omega$ $R_L=4\Omega$ |                                                   | 7  | 12<br>11<br>8<br>6.5 |        | W<br>W<br>W |

|-----------------|-----------------------------|----------------------------------------------------------------------|---------------------------------------------------|----|----------------------|--------|-------------|

| d               | Distortion                  | $P_0 = 0.1 \text{ to } 4W$                                           | $R_L = 3.2\Omega$                                 |    | 0.05                 | 0.5    | %           |

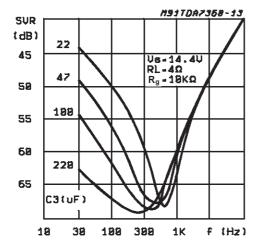

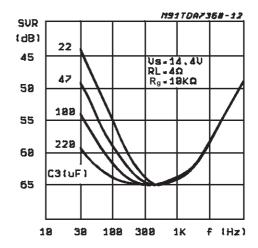

| SVR             | Supply Voltage Rejection    | $R_g = 10K\Omega$<br>f = 100Hz                                       | C3 = 22μF<br>C3 = 100μF                           | 45 | 62                   |        | dB<br>dB    |

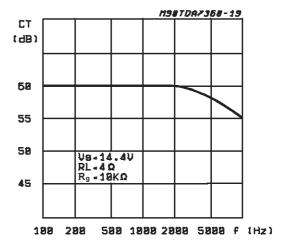

| СТ              | Crosstalk                   | f = 1KHz<br>f = 10KHz                                                |                                                   | 45 | 55                   |        | dB<br>dB    |

| R <sub>I</sub>  | Input Resistance            |                                                                      |                                                   |    | 50                   |        | KΩ          |

| $G_V$           | Voltage Gain                |                                                                      |                                                   |    | 20                   |        | dB          |

| G∨              | Voltage Gain Match          |                                                                      |                                                   |    |                      | 1      | dB          |

| E <sub>IN</sub> | Input Noise Voltage         | 22 Hz to 22KHz                                                       | $R_g = 50\Omega$ $R_g = 10K\Omega$ $R_g = \infty$ |    | 2.5<br>3<br>3.5      | 5<br>7 | μV<br>μV    |

# BRIDGE

| Vos             | Output Offset Voltage    |                                                               |                                       |          |          | 250    | mV       |

|-----------------|--------------------------|---------------------------------------------------------------|---------------------------------------|----------|----------|--------|----------|

| Po              | Output Power             | d = 10%; R <sub>L</sub> = 40<br>d = 10%; R <sub>L</sub> = 3.5 | 16                                    | 20<br>22 |          | W<br>W |          |

| d               | Distortion               | $P_0 = 0.1 \text{ to } 10W;$                                  | $ R_L = 3.2\Omega$                    |          | 0.05     | 1      | %        |

| SVR             | Supply Voltage Rejection | $R_g = 10K\Omega$<br>f = 100Hz                                | C3 = 22μF<br>C3 = 100μF               | 45       | 62       |        | dB<br>dB |

| R <sub>I</sub>  | Input Resistance         |                                                               |                                       |          | 50       |        | ΚΩ       |

| $G_V$           | Voltage Gain             |                                                               |                                       |          | 26       |        | dB       |

| E <sub>IN</sub> | Input Noise Voltage      | 22Hz to 22KHz                                                 | $R_g = 50\Omega$<br>$R_g = 10K\Omega$ |          | 3.5<br>4 |        | μV<br>μV |

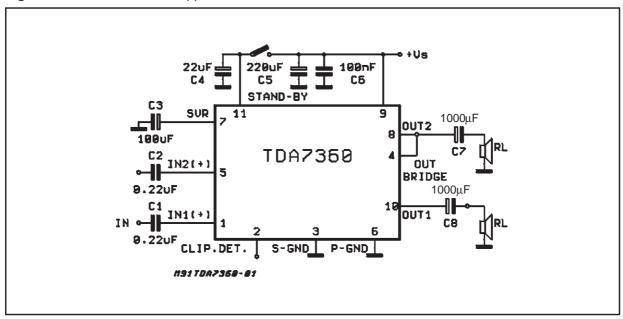

Figure 1: STEREO Test and Application Circuit

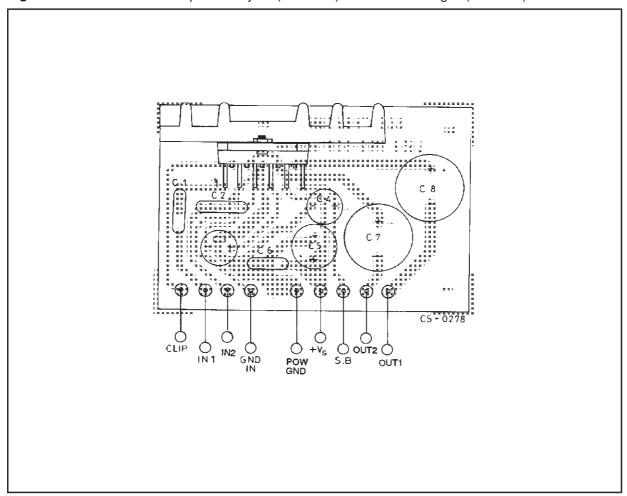

Figure 2: P.C. Board and Component Layout (STEREO) of the circuit of fig. 1 (1:1 scale)

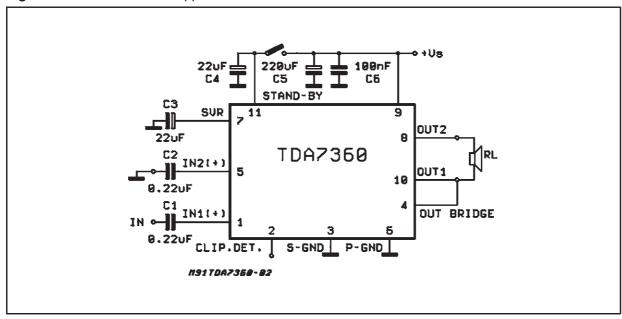

Figure 3: BRIDGE Test and Application Circuit

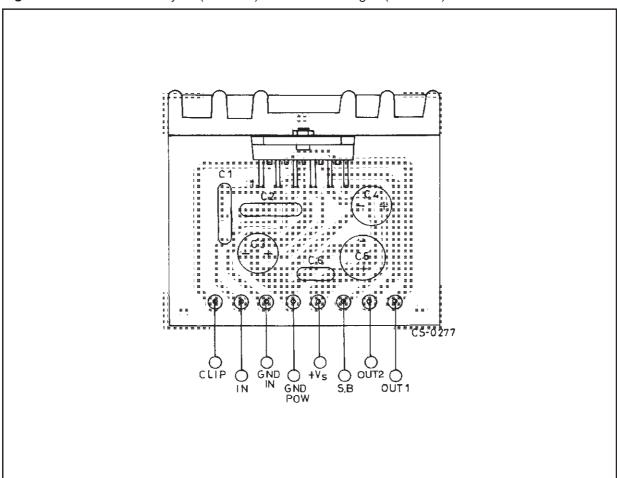

Figure 4: P.C. Board and Layout (BRIDGE) of the circuit of fig. 3 (1:1 scale)

# **RECOMMENDED VALUES OF THE EXTERNAL COMPONENTS** (ref to the Stereo Test and Application Circuit)

| Component | Recommended<br>Value | Purpose                                               | Larger than the Recomm.<br>Value                              | Smaller than the Recomm.<br>Value                                                            |

|-----------|----------------------|-------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| C1        | 0.22μF               | Input<br>Decoupling<br>(CH1)                          |                                                               | I                                                                                            |

| C2        | 0.22μF               | Input<br>Decoupling<br>(CH2)                          | _                                                             |                                                                                              |

| C3        | 100μF                | Supply Voltage<br>Rejection<br>Filtering<br>Capacitor | Longer Turn-On Delay Time                                     | - Worse Supply Voltage Rejection.<br>- Shorter Turn-On Delay Time<br>- Danger of Noise (POP) |

| C4        | 22μF                 | Stand-By<br>ON/OFF<br>Delay                           | Delayed Turn-Off by Stand-By<br>Switch                        | Danger of Noise (POP)                                                                        |

| C5        | 220μF (min)          | Supply By-Pass                                        |                                                               | Danger of Oscillations                                                                       |

| C6        | 100nF (min)          | Supply By-Pass                                        |                                                               | Danger of Oscillations                                                                       |

| C7        | 2200μF               | Output<br>Decoupling<br>CH2                           | - Decrease of Low Frequency Cut Off<br>- Longer Turn On Delay | - Increase of Low Frequency Cut Off<br>- Shorter Turn On Delay                               |

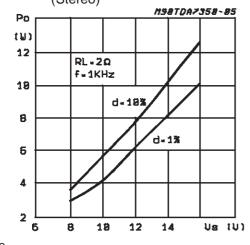

**Figure 5:** Output Power vs. Supply Voltage (Stereo)

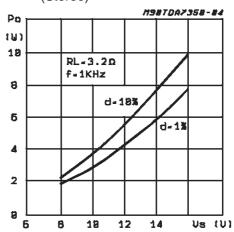

Figure 7: Output Power vs. Supply Voltage (Stereo)

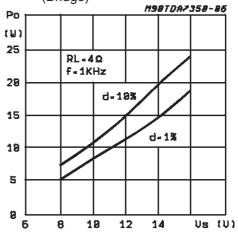

Figure 6: Output Power vs. Supply Voltage (Stereo)

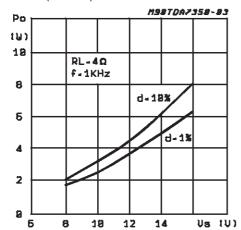

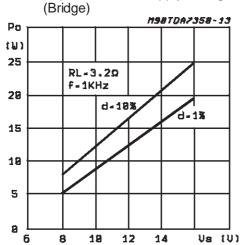

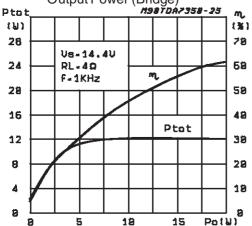

**Figure 8:** Output Power vs. Supply Voltage (Bridge)

57

Figure 9: Output Power vs. Supply Voltage

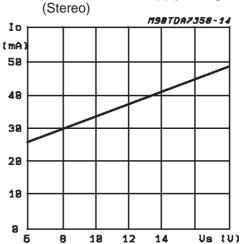

Figure 10: Drain Current vs Supply Voltage

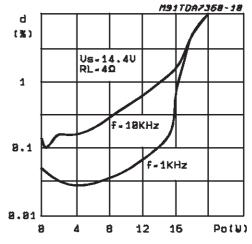

Figure 11: Distortion vs Output Power (Stereo)

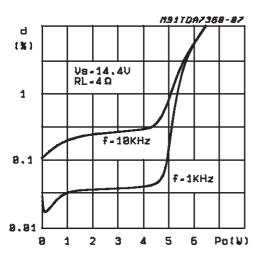

Figure 12: Distortion vs Output Power (Stereo)

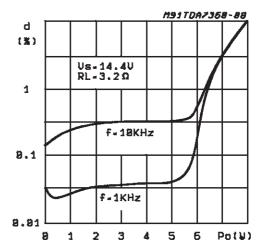

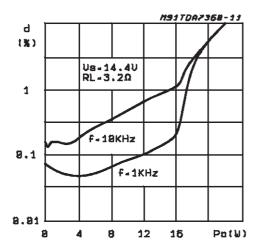

Figure 13: Distortion vs Output Power (Stereo)

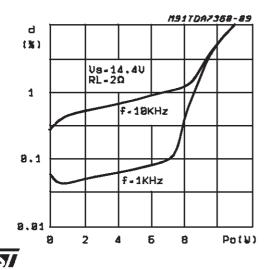

Figure 14: Distortion vs Output Power (Bridge)

Figure 15: Distortion vs. Output Power

Figure 17: SVR vs. Frequency & C<sub>3</sub> (Bridge)

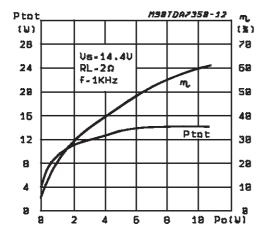

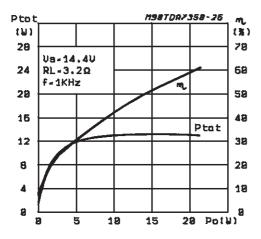

Figure 19: Power Dissipation & Efficiency vs.

Output Power (Stereo)

Figure 16: SVR vs. Frequency & C<sub>3</sub> (Stereo)

Figure 18: Crosstalk vs. Frequency (Stereo)

**Figure 20:** Power Dissipation & Efficiency vs. Output Power (Stereo)

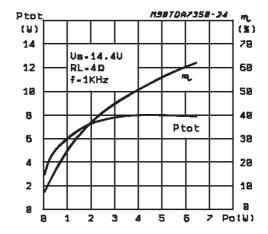

**Figure 22:** Power Dissipation & Efficiency vs. Output Power (Bridge)

#### **AMPLIFIER ORGANIZATION**

The TDA7360 has been developed taking care of the key concepts of the modern power audio amplifier for car radio such as: space and costs saving due to the minimized external count, excellent electrical performances, flexibility in use, superior reliability thanks to a built-in array of protections. As a result the following performances has been achieved:

- NO NEED OF BOOTSTRAP CAPACITORS EVEN AT THE HIGHEST OUTPUT POWER LEVELS

- ABSOLUTE STABILITY WITHOUT EXTER-NAL COMPENSATION THANKS TO THE IN-NOVATIVE OUT STAGE CONFIGURATION, ALSO ALLOWING INTERNALLY FIXED CLOSED LOOP LOWER THAN COMPETI-TORS

- LOW GAIN (20dB STEREO FIXED WITHOUT ANY EXTERNAL COMPONENTS) IN ORDER

- TO MINIMIZE THE OUTPUT NOISE AND OPTIMIZE SVR

- SILENT MUTE/ST-BY FUNCTION FEATUR-ING ABSENCE OF POP ON/OFF NOISE

- HIGH SVR

- STEREO/BRIDGE OPERATION WITHOUT ADDITION OF EXTERNAL COMPONENT

- AC/DC SHORT CIRCUIT PROTECTION (TO GND, TO V<sub>S</sub>, ACROSS THE LOAD)

- LOUDSPEAKER PROTECTION

- DUMP PROTECTION

- ESD PROTECTION

#### **BLOCK DESCRIPTION**

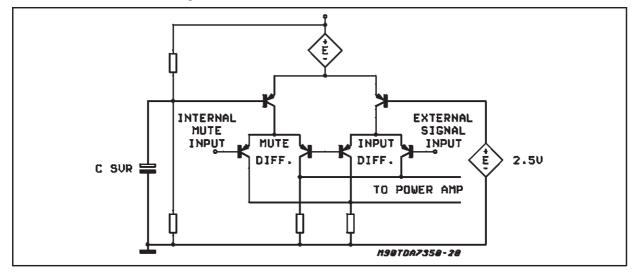

#### **Polarization**

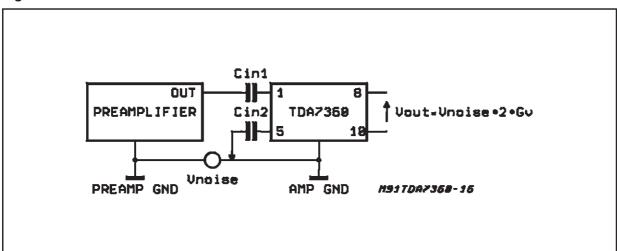

The device is organized with the gain resistors directly connected to the signal ground pin i.e. without gain capacitors (fig. 23).

The non inverting inputs of the amplifiers are connected to the SVR pin by means of resistor dividers, equal to the feedback networks. This allows the outputs to track the SVR pin which is sufficiently slow to avoid audible turn-on and turn-off transients.

#### **SVR**

The voltage ripple on the outputs is equal to the one on SVR pin: with appropriate selection of C<sub>SVR</sub>, more than 60dB of ripple rejection can be obtained.

# **Delayed Turn-on (muting)**

The C<sub>SVR</sub> sets a signal turn-on delay too. A circuit is included which mutes the device until the voltage on SVR pin reaches ~2.5V typ. (fig. 25). The mute function is obtained by duplicating the input differential pair (fig. 24): it can be switched to the signal source or to an internal mute input. This feature is necessary to prevent transients at the inputs reaching the loudspeaker(s) immediately after power-on).

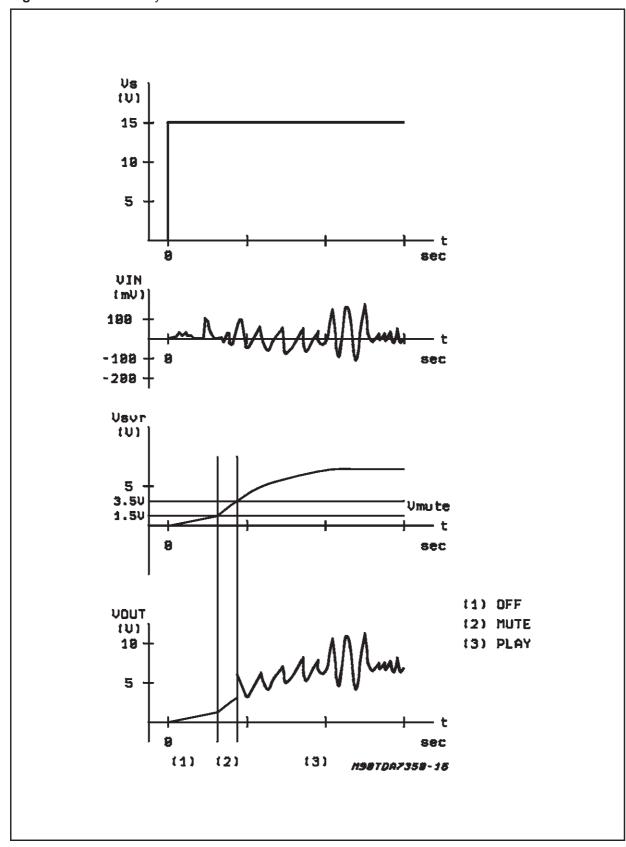

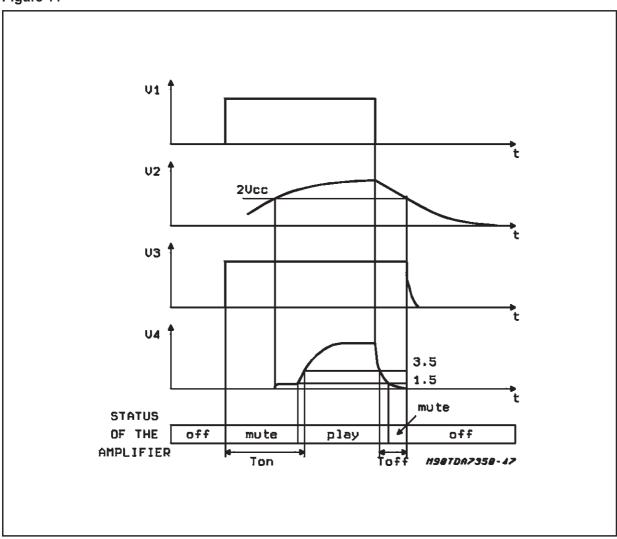

Fig. 25 represents the detailed turn-on transient with reference to the stereo configuration.

At the power-on the output decoupling capacitors are charged through an internal path but the device itself remains switched off (phase 1 of the represented diagram).

When the outputs reach the voltage level of about 1V (this means that there is no presence of short circuits) the device switches on, the SVR capacitor starts charging itself and the output tracks exactly the SVR pin.

During this phase the device is muted until the SVR reaches the "Play" threshold (~2.5V typ.), after that the music signal starts being played.

### Stereo/Bridge Switching

There is also no need for external components for changing from stereo to bridge configuration (figg. 23-26). A simple short circuit between two pins allows phase reversal at one output, yet maintaining the quiescent output voltage.

# Stand-by

The device is also equipped with a stand-by func-

Figure 23: Block Diagram; Stereo Configuration

tion, so that a low current, and hence low cost switch, can be used for turn on/off.

# **Stability**

The device is provided with an internal compensation wich allows to reach low values of closed loop gain.

In this way better performances on S/N ratio and SVR can be obtained.

Figure 24: Mute Function Diagram

Figure 25: Turn-on Delay Circuit

Figure 26: Block Diagram; Bridge Configuration

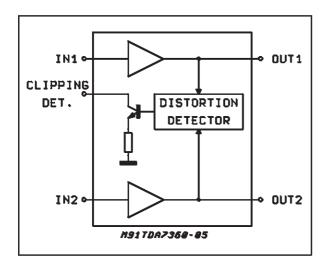

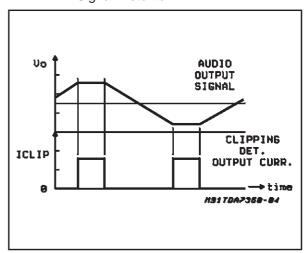

## **CLIP DETECTOR**

The TDA7360 is equipped with an internal circuit able to detect the output stage saturation providing a proper current sinking into an open collector

Figure 27: Dual Channel Distortion Detector

out. (pin2) when a certain distortion level is reached at each output. This particular function allows compression facility whenever the amplifier is overdriven, so obtaining high quality sound at all listening levels.

**Figure 28:** Output at Clipping Detector Pin vs. Signal Distortion

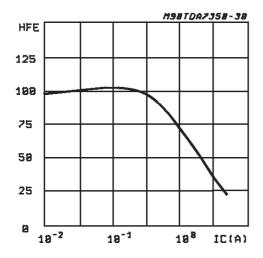

Figure 29: ICV - PNP Gain vs. Ic

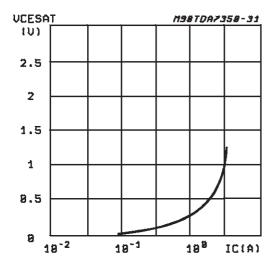

Figure 30: ICV - PNP VCE(sat) vs. IC

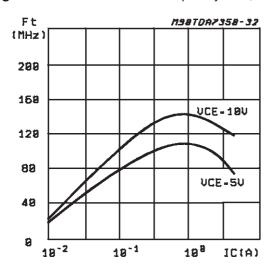

Figure 31: ICV - PNP cut-off frequency vs. Ic

#### **OUTPUT STAGE**

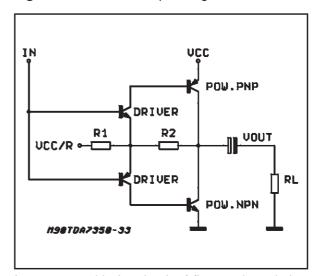

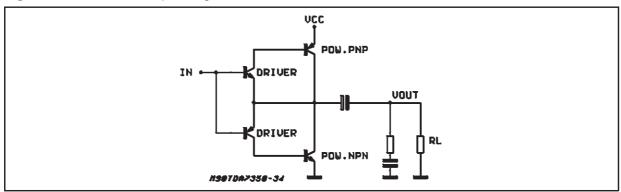

Poor current capability and low cutoff frequency are well known limits of the standard lateral PNP. Composite PNP-NPN power output stages have been widely used, regardless their high saturation drop. This drop can be overcome only at the expense of external components, namely, the bootstrap capacitors. The availability of 4A isolated collector PNP (ICV PNP) adds versatility to the design. The performance of this component, in terms of gain, V<sub>CEsat</sub> and cut-off frequency, is shown in fig. 29, 30, 31 respectively. It is realized in a new bipolar technology, characterized by top-bottom isolation techniques, allowing the implementation of low leakage diodes, too. It guarantees BV<sub>CEO</sub> > 20V and BV<sub>CBO</sub> > 50V both for NPN and PNP transistors. Basically, the connection shown in fig. 32 has been chosen. First of all because its voltage swing is rail-to-rail, limited only by the VCEsat of the output transistors, which are in the range of  $0.3\Omega$  each. Then, the gain VOUT/VIN is greater than unity, approximately 1+R2/R1. (VCC/2 is fixed by an auxiliary amplifier common to both channel). It is possible, controlling the amount of this local feedback, to force the loop gain (A \* β) to less than unity at frequencies for which the phase shift is 180°. This means that the output buffer is intrinsically stable and not prone to oscillation.

Figure 32: The New Output Stage

In contrast, with the circuit of fig. 33, the solution adopted to reduce the gain at high frequencies is the use of an external RC network.

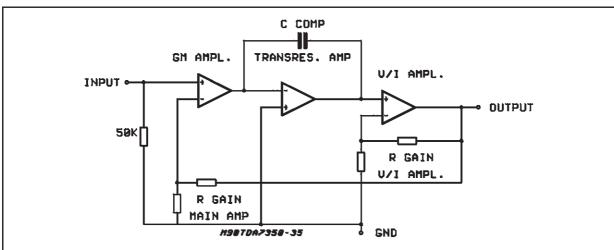

#### **AMPLIFIER BLOCK DIAGRAM**

The block diagram of each voltage amplifier is shown in fig. 34. Regardless of production spread, the current in each final stage is kept low, with enough margin on the minimum, below which cross-over distortion would appear.

Figure 33: A Classical Output Stage

Figure 34: Amplifier Block Diagram

#### **BUILT-IN PROTECTION SYSTEMS**

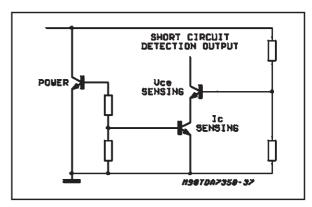

### **Short Circuit Protection**

The maximum current the device can deliver can be calculated by considering the voltage that may be present at the terminals of a car radio amplifier and the minimum load impedance.

Apart from consideration concerning the area of the power transistors it is not difficult to achieve peak currents of this magnitude (5 A peak).

However, it becomes more complicated if AC and DC short circuit protection is also required. In particular, with a protection circuit which limits the output current following the SOA curve of the output transistors it is possible that in some conditions (highly reactive loads, for example) the protection circuit may intervene during normal operation. For this reason each amplifier has been equipped with a protection circuit that intervenes when the output current exceeds 4A

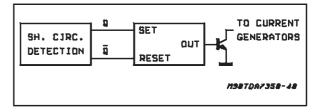

Fig 35 shows the protection circuit for an NPN power transistor (a symmetrical circuit applies to PNP). The VBE of the power is monitored and gives out a signal, available through a cascode.

This cascode is used to avoid the intervention of the short circuit protection when the saturation is below a given limit.

The signal sets a flip-flop which forces the amplifier outputs into a high impedance state.

In case of DC short circuit when the short circuit is removed the flip-flop is reset and restarts the circuit (fig. 39). In case of AC short circuit or load shorted in Bridge configuration, the device is continuously switched in ON/OFF conditions and the current is limited.

Figure 35: Circuitry for Short Circuit Detection

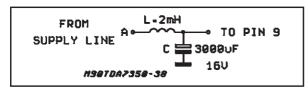

### **Load Dump Voltage Surge**

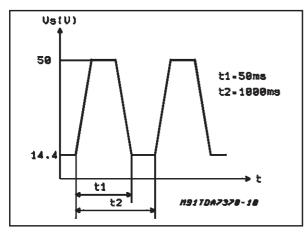

The TDA 7360 has a circuit which enables it to withstand a voltage pulse train on pin 9, of the type shown in fig. 37.

If the supply voltage peaks to more than 50V, then an LC filter must be inserted between the supply and pin 9, in order to assure that the pulses at pin 9 will be held within the limits shown.

A suggested LC network is shown in fig. 36. With this network, a train of pulses with amplitude up to 120V and width of 2ms can be applied at point A. This type of protection is ON when the supply voltage (pulse or DC) exceeds 18V. For this reason the maximum operating supply voltage is 18V.

Figure 36

Figure 37

# **Polarity Inversion**

High current (up to 10A) can be handled by the device with no damage for a longer period than the blow-out time of a quick 2A fuse (normally connected in series with the supply). This features is added to avoid destruction, if during fitting to the car, a mistake on the connection of the supply is made.

# **Open Ground**

When the radio is in the ON condition and the ground is accidentally opened, a standard audio amplifier will be damaged. On the TDA7360 protection diodes are included to avoid any damage.

# **DC Voltage**

The maximum operating DC voltage for the TDA7360 is 18V.

However the device can withstand a DC voltage up to 28V with no damage. This could occur dur-

ing winter if two batteries are series connected to crank the engine.

# **Thermal Shut-down**

The presence of a thermal limiting circuit offers the following advantages:

- an overload on the output (even if it is permanent), or an excessive ambient temperature can be easily withstood.

- 2)the heatsink can have a smaller factor of safety compared with that of a conventional circuit. There is no device damage in the case of excessive junction temperature: all happens is that P<sub>o</sub> (and therefore P<sub>tot</sub>) and I<sub>d</sub> are reduced.

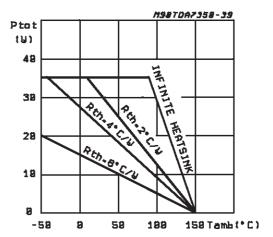

The maximum allowable power dissipation depends upon the size of the external heatsink (i.e. its thermal resistance); Fig. 38 shows the dissipable power as a function of ambient temperature for different thermal resistance.

Figure 38: Maximum Allowable Power

Dissipation vs. Ambient Temperature

## **Loudspeaker Protection**

The TDA7360 guarantees safe operations even for the loudspeaker in case of accidental shortcircuit.

Whenever a single OUT to GND, OUT to Vs short circuit occurs both the outputs are switched OFF so limiting dangerous DC current flowing through the loudspeaker.

Figure 39: Restart Circuit

### **APPLICATION HINTS**

This section explains briefly how to get the best from the TDA7360 and presents some application circuits with suggestions for the value of the components. These values can change depending on the characteristics that the designer of the car radio wants to obtain, or other parts of the car radio that are connected to the audio block.

To optimize the performance of the audio part it is useful (or indispensable) to analyze also the parts outside this block that can have an interconnection with the amplifier.

This method can provide components and system cost saving.

### **Reducing Turn On-Off Pop**

The TDA7360 has been designed in a way that the turn on(off) transients are controlled through the charge(discharge) of the Csvr capacitor.

As a result of it, the turn on(off) transient spectrum contents is limited only to the subsonic range. The following section gives some brief notes to get the best from this design feature(it will refer mainly to the stereo application which appears to be in most cases the more critical from the pop viewpoint. The bridge connection in fact, due to the common mode waveform at the outputs, does not give pop effect).

#### **TURN-ON**

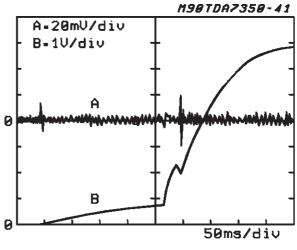

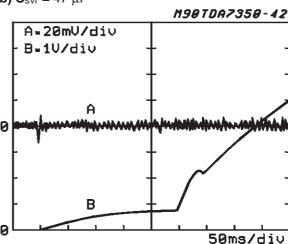

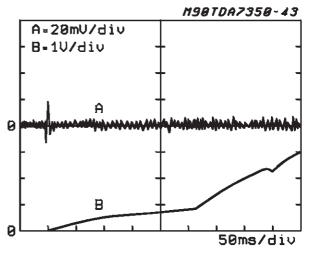

Fig 40 shows the output waveform (before and after the "A" weighting filter) compared to the value of Csvr.

Better pop-on performance is obtained with higher Csvr values (the recommended range is from 22uF to 220uF).

The turn-on delay (during which the amplifier is in mute condition) is a function essentially of :  $C_{\text{out}}$ ,  $C_{\text{svr}}$ .

Being:

$$T1 \approx 120 \bullet C_{out}$$

$T2 \approx 1200 \bullet C_{svr}$

The turn-on delay is given by:

The best performance is obtained by driving the st-by pin with a ramp having a slope slower than 2V/ms

# Figure 40:

**a)**  $C_{svr} = 22 \mu F$

**b)**  $C_{svr} = 47 \mu F$

**c)**  $C_{svr} = 100 \mu F$

### **TURN-OFF**

A turn-off pop can occur if the st-by pin goes low with a short time constant (this can occur if other car radio sections, preamplifiers,radio.. are supplied through the same st-by switch).

This pop is due to the fast switch-off of the internal current generator of the amplifier.

If the voltage present across the load becomes rapidly zero (due to the fast switch off) a small pop occurs, depending also on Cout, Rload.

The parameters that set the switch off time constant of the st-by pin are:

- the st-by capacitor (Cst-by)

- ♦ the SVR capacitor (Csvr)

- resistors connected from st-by pin to ground (Rext)

The time constant is given by:

$T \approx \text{Csvr} \bullet 2000\Omega \text{ // Rext} + \text{Cst-by} \bullet 2500\Omega \text{ // Rext}$ The suggested time constants are :

T > 120ms with  $C_{out}=1000\mu F$ ,  $R_L=40$ hm, stereo

T > 170ms with  $C_{out}=2200\mu F$ ,  $R_L=40$ hm, stereo

If Rext is too low the Csvr can become too high and a different approach may be useful (see next section).

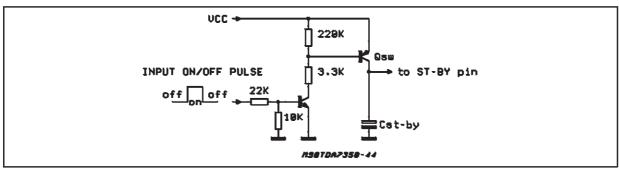

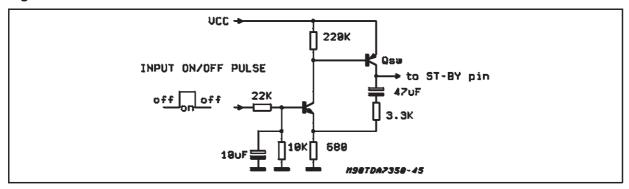

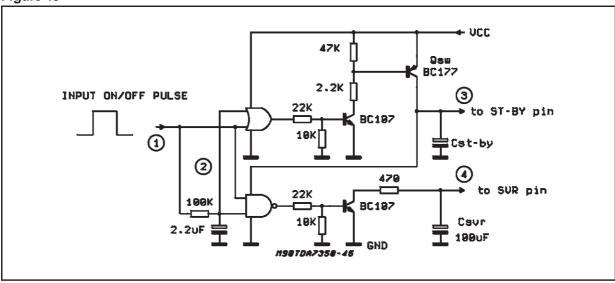

Figg 41, 42 show some types of electronic switches ( $\mu$ P compatible) suitable for supplying the st-by pin (it is important that Qsw is able to saturate with V<sub>CE</sub>  $\leq$  150mV),

Also for turn off pop the bridge configuration is su-

perior, in particular the st-by pin can go low faster.

# GLOBAL APPROACH TO SOLVING POP PROBLEM BY USING THE MUTING/TURN ON DELAY FUNCTION

In the real case turn-on and turn-off pop problems are generated not only by the power amplifier,but also (very often) by preamplifiers,tone controls,radios etc. and transmitted by the power amplifier to the loudspeaker.

A simple approach to solving these problems is to use the mute characteristics of the TDA7360.

If the SVR pin is at a voltage below 1.5 V, the mute attenuation (typ) is 30dB .The amplifier is in play mode when Vsvr overcomes 3.5 V.

With the circuit of fig 43 we can mute the amplifier for a time Ton after switch-on and for a time Toff after switch-off. During this period the circuitry that precedes the power amplifier can produce spurious spikes that are not transmitted to the loud-speaker. This can give back a very simple design of this circuitry from the pop point of view.

A timing diagram of this circuit is illustrated in fig 44. Other advantages of this circuit are:

- A reduced time constant allowance of stand-by pin turn off.Consequently it is possible to drive all the car-radio with the signal that drives this pin.

- -A better turn-off noise with signal on the output.

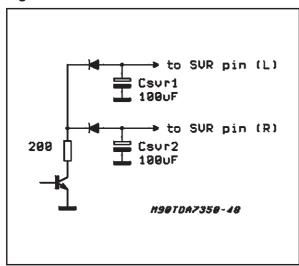

To drive two stereo amplifiers with this circuit it is possible to use the circuit of fig 45.

Figure 41

Figure 42

Figure 43

Figure 44

Figure 45

**BALANCED INPUT IN BRIDGE CONFIGURATION**A helpful characteristic of the TDA7360 is that,in

bridge configuration, a signal present on both the input capacitors is amplified by the same amount and it is present in phase at the outputs, so this signal does not produce effects on the load. The typical value of CMRR is 46 dB.

Looking at fig 46, we can see that a noise signal from the ground of the power amplifier to the ground of the hypothetical preamplifier is amplified of a factor equal to the gain of the amplifier (2 \* Gy).

Using a configuration of fig. 47 the same ground noise is present at the output multiplied by the factor 2  $^{\star}$  Gv/200.

This means less distortion,less noise (e.g. motor cassette noise) and/or a simplification of the layout of PC board.

The only limitation of this balanced input is the maximum amplitude of common mode signals (few tens of millivolt) to avoid a loss of output power due to the common mode signal on the output, but in a large number of cases this signal is within this range.

Figure 46

Figure 47

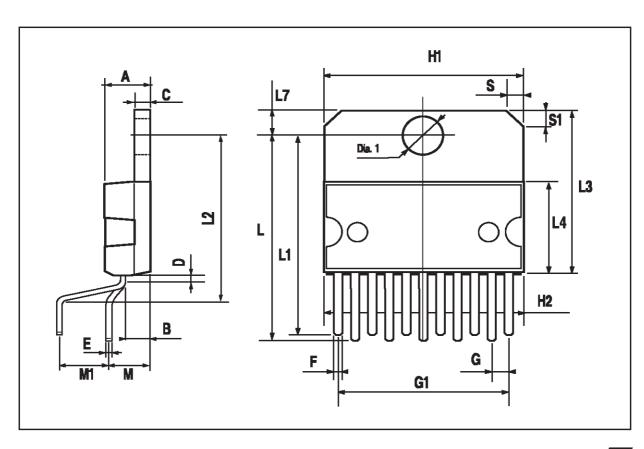

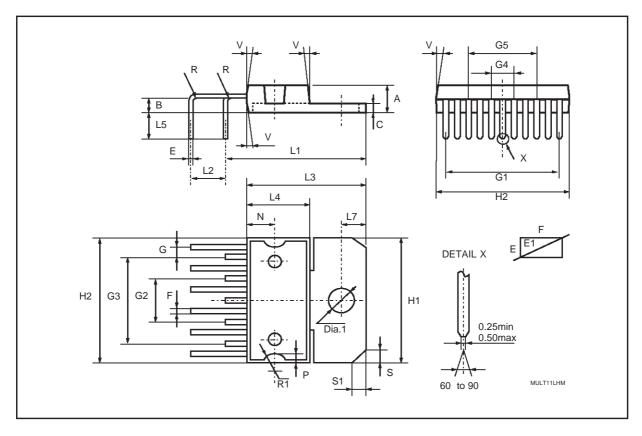

| DIM.   |       | mm inch |       |       |       |       |

|--------|-------|---------|-------|-------|-------|-------|

| DIIVI. | MIN.  | TYP.    | MAX.  | MIN.  | TYP.  | MAX.  |

| Α      |       |         | 5     |       |       | 0.197 |

| В      |       |         | 2.65  |       |       | 0.104 |

| С      |       |         | 1.6   |       |       | 0.063 |

| D      |       | 1       |       |       | 0.039 |       |

| E      | 0.49  |         | 0.55  | 0.019 |       | 0.022 |

| F      | 0.88  |         | 0.95  | 0.035 |       | 0.037 |

| G      | 1.45  | 1.7     | 1.95  | 0.057 | 0.067 | 0.077 |

| G1     | 16.75 | 17      | 17.25 | 0.659 | 0.669 | 0.679 |

| H1     | 19.6  |         |       | 0.772 |       |       |

| H2     |       |         | 20.2  |       |       | 0.795 |

| L      | 21.9  | 22.2    | 22.5  | 0.862 | 0.874 | 0.886 |

| L1     | 21.7  | 22.1    | 22.5  | 0.854 | 0.87  | 0.886 |

| L2     | 17.4  |         | 18.1  | 0.685 |       | 0.713 |

| L3     | 17.25 | 17.5    | 17.75 | 0.679 | 0.689 | 0.699 |

| L4     | 10.3  | 10.7    | 10.9  | 0.406 | 0.421 | 0.429 |

| L7     | 2.65  |         | 2.9   | 0.104 |       | 0.114 |

| М      | 4.25  | 4.55    | 4.85  | 0.167 | 0.179 | 0.191 |

| M1     | 4.73  | 5.08    | 5.43  | 0.186 | 0.200 | 0.214 |

| S      | 1.9   |         | 2.6   | 0.075 |       | 0.102 |

| S1     | 1.9   |         | 2.6   | 0.075 |       | 0.102 |

| Dia1   | 3.65  |         | 3.85  | 0.144 |       | 0.152 |

# OUTLINE AND MECHANICAL DATA

| DIM           |       | mm    |       |       | inch  |        |

|---------------|-------|-------|-------|-------|-------|--------|

| DIM.          | MIN.  | TYP.  | MAX.  | MIN.  | TYP.  | MAX.   |

| Α             | 4.373 | 4.5   | 4.627 | 0.172 | 0.177 | 0.182  |

| В             |       |       | 2.65  |       |       | 0.104  |

| С             |       |       | 1.6   |       |       | 0.063  |

| Е             | 0.49  | 0.515 | 0.55  | 0.019 | 0.020 | 0.022  |

| E1            | 1.007 | 1.037 | 1.07  | 0.040 | 0.041 | 0.042  |

| F             | 0.88  | 0.9   | 0.95  | 0.035 | 0.035 | 0.037  |

| G             | 1.5   | 1.7   | 1.9   | 0.059 | 0.067 | 0.075  |

| G.1           | 16.82 | 17.02 | 17.22 | 0.662 | 0.670 | 0.678  |

| G2            | 6.61  | 6.807 | 7.01  | 0.260 | 0.268 | 0.276  |

| G3            | 13.41 | 13.61 | 13.81 | 0.528 | 0.536 | 13.810 |

| G4            | 3.2   | 3.4   | 3.6   | 0.126 | 0.134 | 0.142  |

| G5            | 10.01 | 10.21 | 10.41 | 0.394 | 0.402 | 0.410  |

| H1            | 19.6  |       |       | 0.772 |       |        |

| H2            |       |       | 20.2  |       |       | 0.795  |

| L1            | 19.28 | 19.58 | 19.88 | 0.759 | 0.771 | 0.783  |

| L2            | 3.61  | 3.81  | 4.01  | 0.142 | 0.150 | 0.158  |

| L3            | 17.25 | 17.5  | 17.75 | 0.679 | 0.689 | 0.699  |

| L4            | 10.3  | 10.6  | 10.9  | 0.406 | 0.417 | 0.429  |

| L5<br>(Inner) | 3.4   | 3.75  | 4     | 0.134 | 0.148 | 0.157  |

| L5<br>(Outer) | 3.6   | 3.9   | 4.2   | 0.142 | 0.154 | 4.200  |

| L7            | 2.65  |       | 2.9   | 0.104 |       | 0.114  |

| R             | 0.75  | 1     | 1.25  | 0.030 | 0.039 | 0.049  |

| S             | 1.9   |       | 2.6   | 0.075 |       | 0.102  |

| S1            | 1.9   |       | 2.6   | 0.075 |       | 0.102  |

| Dia1          | 3.65  |       | 3.85  | 0.144 |       | 0.152  |

# OUTLINE AND MECHANICAL DATA

Multiwatt11 H (Short leads)

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

MULTIWATT® is a Registered Trademark of the STMicroelectronics

© 1998 STMicroelectronics – Printed in Italy – All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com