# 1:3 Clock Buffer

## **General Description**

The SLG3SY3952 uses a single input 26 MHz clock source to provide three 26 MHz clock outputs.

#### **Features**

- 1.8 V VDD operation

- Current Consumption: 1.0 mA

- OE for 26M\_A, 26M\_B and 26M\_C

- · Supports Industrial temperature range

- Improved performance over temperature

- · Smaller package and layout foot print

- 10-pin STDFN: 1.0 x 2.0 x 0.55 mm, 0.4 mm pitch

- Pb-Free / Halogen-Free / RoHS compliant

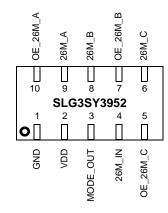

# **Pin Configuration**

10-pin STDFN (Top View)

# **Output Summary**

• 3x 26 MHz clock outputs

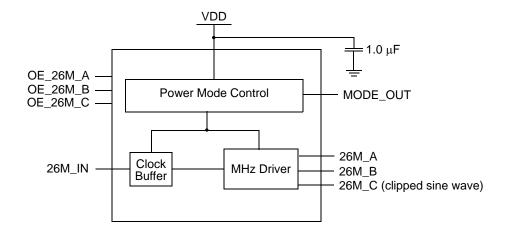

## **Block Diagram**

# **SLG3SY3952**

# **Pin Description**

| Pin # | Pin Name | Type <sup>1</sup> | Pin Description                                                                                                                                                                    |  |

|-------|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | GND      | GND               | Ground                                                                                                                                                                             |  |

| 2     | VDD      | PWR               | <b>Power Supply:</b> 1.8 V as main power supply. 1.0 $\mu\text{F}$ decoupling capacitor is recommended.                                                                            |  |

| 3     | MODE_OUT | O, SE             | <b>Mode:</b> 1.8 V CMOS output signal that identifies the mode SLG3SY3952 is in. May be used as clock request. PMOS Open Drain output. Requires 100 k $\Omega$ pull down resistor. |  |

| 4     | 26M_IN   | I                 | Clock Input: 26 MHz clock input.                                                                                                                                                   |  |

| 5     | OE_26M_C | I                 | <b>Output Enable:</b> Output enable for the 26M_C output as well as the control signor the Power Mode switching.                                                                   |  |

| 6     | 26M_C    | O, SE             | Clock Output: 26 MHz output (Stop by OE_26M_C)                                                                                                                                     |  |

| 7     | OE_26M_B | I                 | Output Enable: Output enable for the 26M_B output as well as the control sign for the Power Mode switching.                                                                        |  |

| 8     | 26M_B    | O, SE             | Clock Output: 26 MHz output (Stop by OE_26M_B)                                                                                                                                     |  |

| 9     | 26M_A    | O, SE             | Clock Output: 26 MHz output (Stop by OE_26M_A)                                                                                                                                     |  |

| 10    | OE_26M_A | I                 | Output Enable: Output enable for the 26M_C output as well as the control signal for the Power Mode switching.                                                                      |  |

#### Notes:

- 1. Type Definitions

- PWR: power

- GND: ground

- I: input

- O: output

- SE: single ended signal

# CMOS Input Specifications (OE<sup>1</sup>)

$T_A = 25$  °C (unless otherwise stated)

| Symbol          | Description        | Conditions | Min | Тур | Max | Unit |

|-----------------|--------------------|------------|-----|-----|-----|------|

| V <sub>IH</sub> | Input Voltage HIGH |            | 1.5 |     |     | V    |

| $V_{IL}$        | Input Voltage LOW  |            |     |     | 0.3 | V    |

#### Notes:

1.  $V_{OE} < V_{DD} + 0.3 \text{ V}$  must be met at all times including power up, where  $V_{OE}$  is the voltage on OE pin and  $V_{DD}$  is the voltage on VDD pin.

000-003SY3952-04 Page 2 of 10

## 26 MHz Clock Output Characteristics (26M)

$T_A$  = 25 °C,  $V_{DD}$  = 1.8 V (unless otherwise stated)

| Symbol                         | Description                                | Conditions                                                   | Min                      | Тур | Max                      | Unit |

|--------------------------------|--------------------------------------------|--------------------------------------------------------------|--------------------------|-----|--------------------------|------|

| F <sub>INI</sub>               | Initial Frequency                          |                                                              | 5                        |     | 50                       | MHz  |

| DC                             | Duty Cycle                                 | 0.5 x V <sub>DD</sub>                                        | 45                       | 50  | 55                       | %    |

| V <sub>OH</sub>                | Output Voltage HIGH                        | I <sub>OH</sub> = 1 mA                                       | 0.8 x<br>V <sub>DD</sub> | 2   |                          | ٧    |

| V <sub>OL</sub>                | Output Voltage LOW                         | I <sub>OL</sub> = -1 mA                                      |                          | 2   | 0.2 x<br>V <sub>DD</sub> | ٧    |

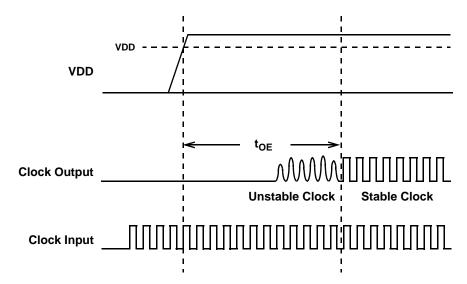

| t <sub>PU</sub> 3,5            | Power Up Delay (t <sub>PU,MHz</sub> )      | See Note 3 & 5                                               |                          | 3   | 5                        | μS   |

| t <sub>OE</sub> <sup>4,5</sup> | Output Enable Delay (t <sub>OE,MHz</sub> ) | See Note 4 & 5                                               | 0                        | 1.0 | 2.0                      | μS   |

| t <sub>R</sub>                 | Rise Time                                  | measured between V <sub>OH,min</sub> and V <sub>OL,max</sub> |                          | TBD |                          | ns   |

| t <sub>F</sub>                 | Fall Time                                  | measured between $V_{OH,min}$ and $V_{OL,max}$               |                          | TBD |                          | ns   |

| CL                             | Output Load Capacitance                    |                                                              |                          | 8   | 10                       | pF   |

#### Notes:

- 1. This parameter tracks Reference Crystal characteristics.

- 2.  $V_{OH} = 1.0 \text{ x } V_{DD}$  (typ) and  $V_{OL} = 0 \text{ V}$  (typ) when driving a fully capacitive load, i.e.  $I_{OH} = I_{OL} = 0 \text{ mA}$ .

- 3. This parameter is applicable when the device powers up into Active Mode (OE = VDD during power up) or transitions into Active Mode immediately after power up. The delay time is referenced from the point where V<sub>DD</sub> ≥ V<sub>DD,min</sub> is met to the 26 MHz output being stable and valid. If OE is left floating, t<sub>PU</sub> may be longer.

- This parameter is applicable when the device enters Active Mode from Hibernate Mode during normal operation. The delay time is referenced from the point where OE ≥ V<sub>IH,min</sub> is met to the 26 MHz output being stable and valid.

- 5. Both t<sub>PU</sub> and t<sub>OE</sub> should be satisfied in order for the 26 MHz output to be stable and valid.

000-003SY3952-04 Page 3 of 10

# **SLG3SY3952**

# **Power Supply Electrical Specifications (VDD)**

$T_A = 25 \, ^{\circ}C$

| Symbol                       | Description                         | Conditions              | Min | Тур | Max | Unit |

|------------------------------|-------------------------------------|-------------------------|-----|-----|-----|------|

| V <sub>DD</sub> <sup>1</sup> | Operating Voltage for VDD           |                         | 1.7 | 1.8 | 1.9 | V    |

| $I_{VDD}^2$                  | V <sub>DD</sub> current consumption | V <sub>DD</sub> = 1.8 V |     | 1.0 |     | mA   |

V<sub>OE</sub> < V<sub>DD</sub> + 0.3 V must be met at all times including power up, where V<sub>OE</sub> is the voltage on OE pin and V<sub>DD</sub> is the voltage on VDD pin.

Average current depends on application and output load. Specified values are for No Load condition.

000-003SY3952-04 Page 4 of 10

# **Timing Diagrams**

# **Output Enable Delay (26 MHz Output)**

000-003SY3952-04 Page 5 of 10

# **Package Top Marking System Definition**

000-003SY3952-04 Page 6 of 10

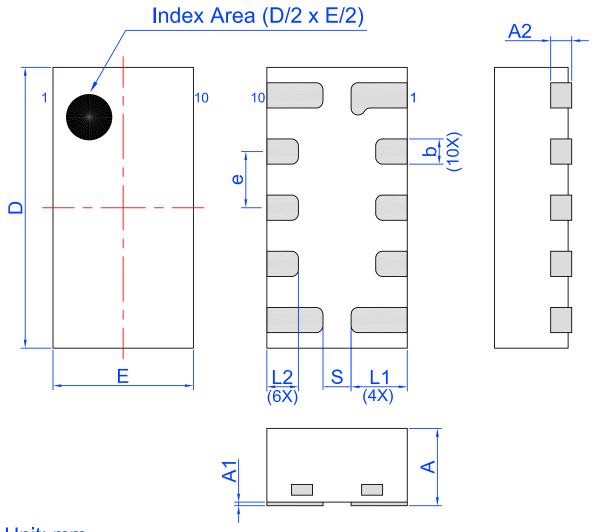

# **Package Drawing and Dimensions**

## 10 Lead STDFN Package JEDEC MO-252

# Unit: mm

| Symbol | Min      | Nom. | Max   | Symbol | Min   | Nom.    | Max   |

|--------|----------|------|-------|--------|-------|---------|-------|

| Α      | 0.50     | 0.55 | 0.60  | D      | 1.95  | 2.00    | 2.05  |

| A1     | 0.005    | _    | 0.060 | E      | 0.95  | 1.00    | 1.05  |

| A2     | 0.10     | 0.15 | 0.20  | L1     | 0.35  | 0.40    | 0.45  |

| b      | 0.13     | 0.18 | 0.23  | L2     | 0.175 | 0.225   | 0.275 |

| е      | 0.40 BSC |      |       | S      |       | 0.2 REF |       |

000-003SY3952-04 Page 7 of 10

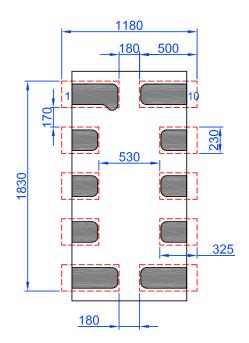

# **Recommended Land Pattern**

# Units: µm

# **Recommended Reflow Soldering Profile**

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 1.10 mm<sup>3</sup> (nominal). More information can be found at www.jedec.org.

000-003\$Y3952-04 Page 8 of 10

# **SLG3SY3952**

# **Ordering Information**

| Part Number   | Туре                         | Production Flow             |  |

|---------------|------------------------------|-----------------------------|--|

| SLG3SY3952V   | 10-pin STDFN                 | Industrial, -40 °C to 85 °C |  |

| SLG3SY3952VTR | 10-pin STDFN (Tape and Reel) | Industrial, -40 °C to 85 °C |  |

000-003SY3952-04 Page 9 of 10

### Silego Website & Support

#### Silego Technology Website

Silego Technology provides online support via our website at <a href="http://www.silego.com/">http://www.silego.com/</a>. This website is used as a means to make files and information easily available to customers.

For more information regarding Silego Green products, please visit:

http://greenpak.silego.com/ http://greenfet.silego.com/ http://greenpak2.silego.com/ http://greenfet2.silego.com/ http://greenclk.silego.com/

Products are also available for purchase directly from Silego at the Silego Online Store at http://store.silego.com/.

#### Silego Technical Support

Datasheets and errata, application notes and example designs, user guides, and hardware support documents and the latest software releases are available at the Silego website or can be requested directly at <a href="mailto:info@silego.com">info@silego.com</a>.

For specific GreenPAK design or applications questions and support please send e-mail requests to GreenPAK@silego.com

Users of Silego products can receive assistance through several channels:

#### **Online Live Support**

Silego Technology has live video technical assistance and sales support available at <a href="http://www.silego.com/">http://www.silego.com/</a>. Please ask our live web receptionist to schedule a 1 on 1 training session with one of our application engineers.

#### Contact Your Local Sales Representative

Customers can contact their local sales representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. More information regarding your local representative is available at the Silego website or send a request to <a href="mailto:info@silego.com">info@silego.com</a>

#### **Contact Silego Directly**

Silego can be contacted directly via e-mail at info@silego.com or user submission form, located at the following URL:

http://support.silego.com/

#### Other Information

The latest Silego Technology press releases, listing of seminars and events, listings of world wide Silego Technology offices and representatives are all available at <a href="http://www.silego.com/">http://www.silego.com/</a>

THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. SILEGO TECHNOLOGY DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. SILEGO TECHNOLOGY RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN, FUNCTIONS AND RELIABILITY WITHOUT NOTICE.

000-003SY3952-04 Page 10 of 10